- 您现在的位置:买卖IC网 > Sheet目录2000 > IDTSSTE32882HLBBKG (IDT, Integrated Device Technology Inc)IC REGISTERING CLK DRIVER 176BGA

1.35V/1.5V REGISTERING CLOCK DRIVER WITH PARITY TEST AND QUAD CHIP SELECT

13

SSTE32882HLB

7201/14

SSTE32882HLB

1.35V/1.5V REGISTERING CLOCK DRIVER WITH PARITY TEST AND QUAD CHIP SELECT

COMMERCIAL TEMPERATURE

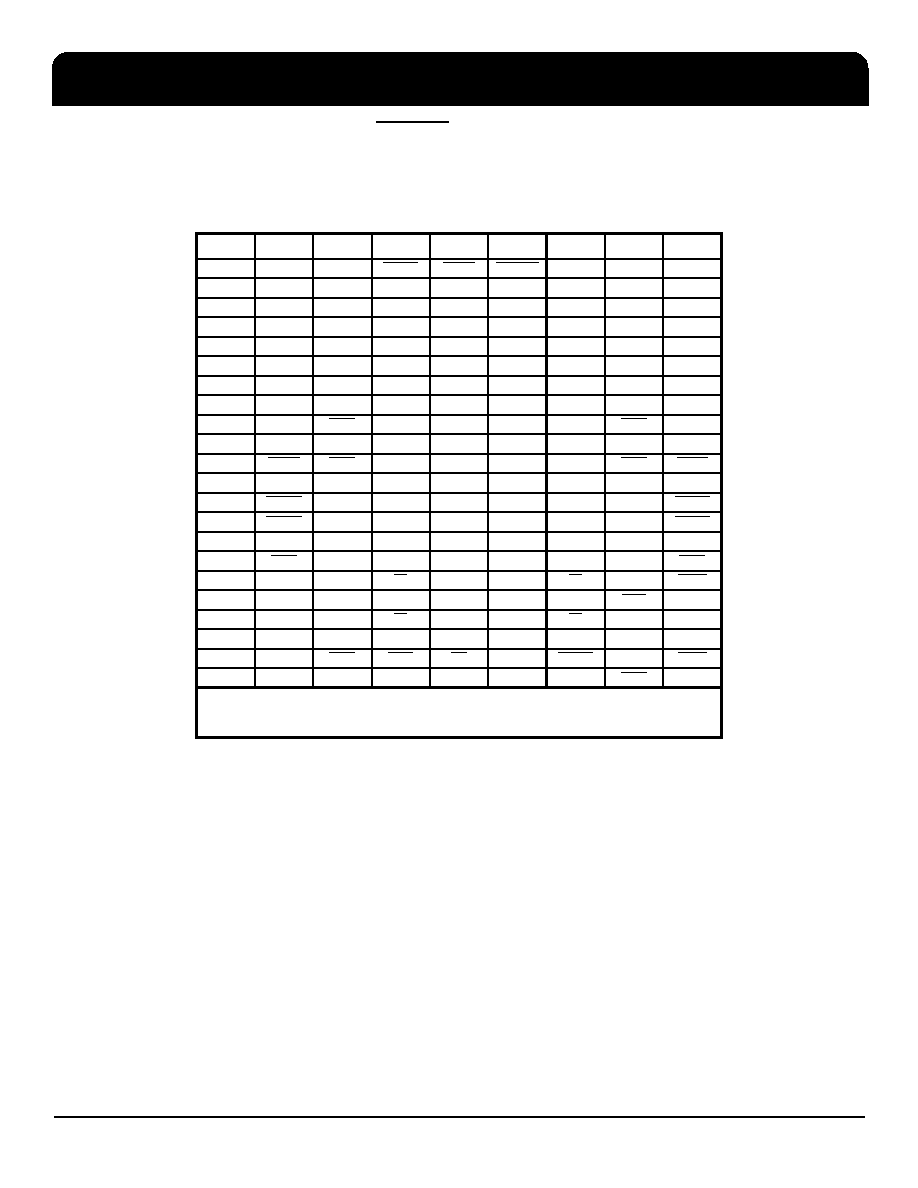

Ball Assignment; MIRROR=LOW, QCSEN=LOW

The table below specifies the pinout for SSTE32882 in front configuration with QuadCS mode enabled.

1

2345678

A

QAA13

QAA8

QCSEN

RESET

ERROUT

RSVD

QBA8

QBA13

B

QAA14

QAA7

VSS

MIRROR

VSS

QBA7

QBA14

C

QAA9

QAA6

VDD

QBA6

QBA9

D

QAA11

QAA5

VSS

QBA5

QBA11

E

QAA2

QAA4

VDD

QBA4

QBA2

F

QAA1

QAA3

VSS

QBA3

QBA1

G

QAA0

QABA1

VDD

QBBA1

QBA0

H

QAA12

QABA0

VSS

QBBA0

QBA12

J

QABA2

QCS1

VDD

QCS3

QBBA2

K

QAA15

QACKE0

VSS

QBCKE0

QBA15

L

QAWE

QCS0

VDD

QCS2

QBWE

M

QAA10

QACKE1

VSS

QBCKE1

QBA10

N

QACAS

QAODT0

VDD

QBODT0

QBCAS

P

QARAS

QAODT1

VSS

QBODT1

QBRAS

R

DA14

DCKE1

VDD

DODT1

DA10

T

DCS0

DCKE0

VSS

DODT0

DCS1

U

DA12

DA3

Y1

PVSS

PVDD

Y0

DA4

DCAS

V

DA5

DA9

Y1

PVSS

PVDD

Y0

DWE

DA2

W

DA8

DA15

Y3

PVSS

PVDD

Y2

DA1

DBA0

Y

DA7

DBA2

Y3

AVSS

AVDD

Y2

DA13

DBA1

AA

DA11

DCS2

FBIN

CK

RSVD

FBOUT

PAR_IN

DRAS

AB

DA6

RSVD

FBIN

CK

VREFCA

FBOUT

DCS3

DA0

Pins A6, AA5 and AB2 are reserved for future functions must not be connected on system. The system

must provide a solder pad for these pins. The device design needs to tolerate floating on these pins. A3

must be tied LOW for this configuration.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDTSSTE32882KA1AKG

IC REGISTERING CLK DRIVER 176BGA

ISD1750SYR

IC VOICE REC/PLAY 50SEC 28-SOIC

ISD5008EYI

IC VOICE REC/PLAY 4-8MIN 28-TSOP

ISL12008IB8Z

IC RTC I2C LO-POWER 8-SOIC

ISL12020MIRZ-T7A

IC RTC/CALENDAR TEMP SNSR 20DFN

ISL12022IBZ-T7A

IC RTC/CALENDAR TEMP SNSR 8SOIC

ISL12022MAIBZ

IC RTC/CALENDAR TEMP SNSR 20SOIC

ISL12022MIBZ-T7A

IC RTC/CALENDAR TEMP SNSR 20SOIC

相关代理商/技术参数

IDTSSTE32882HLBBKG8

制造商:Integrated Device Technology Inc 功能描述:IC REGISTERING CLK DRIVER 176BGA

IDTSSTE32882KA1AKG

功能描述:IC REGISTERING CLK DRIVER 176BGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTSSTE32882KA1AKG8

制造商:Integrated Device Technology Inc 功能描述:IC REGISTERING CLK DRIVER 176BGA

IDTSSTUB32866BHLF

功能描述:IC BUFFER 25BIT CONF REG 96LFBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1

IDTSSTUB32S869AHLF

功能描述:IC REGISTERED BUFFER 150-TFBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 信号缓冲器,中继器,分配器 系列:- 标准包装:160 系列:- 类型:转发器 Tx/Rx类型:以太网 延迟时间:- 电容 - 输入:- 电源电压:2.37 V ~ 2.63 V 电流 - 电源:60mA 安装类型:表面贴装 封装/外壳:64-TQFP 裸露焊盘 供应商设备封装:64-TQFP-EP(10x10) 包装:托盘 其它名称:Q5134101

IDTSSTUB32S869AHLFT

功能描述:IC REGISTERED BUFFER 150-TFBGA RoHS:是 类别:集成电路 (IC) >> 接口 - 信号缓冲器,中继器,分配器 系列:- 标准包装:160 系列:- 类型:转发器 Tx/Rx类型:以太网 延迟时间:- 电容 - 输入:- 电源电压:2.37 V ~ 2.63 V 电流 - 电源:60mA 安装类型:表面贴装 封装/外壳:64-TQFP 裸露焊盘 供应商设备封装:64-TQFP-EP(10x10) 包装:托盘 其它名称:Q5134101

IDTSSTVF16857AGLF

功能描述:IC DDR REGISTER 48-TSSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 标准包装:3,000 系列:- 应用:PDA,便携式音频/视频,智能电话 接口:I²C,2 线串口 电源电压:1.65 V ~ 3.6 V 封装/外壳:24-WQFN 裸露焊盘 供应商设备封装:24-QFN 裸露焊盘(4x4) 包装:带卷 (TR) 安装类型:表面贴装 产品目录页面:1015 (CN2011-ZH PDF) 其它名称:296-25223-2

IDTSTAC9200X3NAEB1X

功能描述:IC AUDIO CODEC 2CH HD 32-QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR)